Received 12 September 2023; revised 22 December 2023 and 31 January 2024; accepted 8 February 2024. Date of publication 15 February 2024; date of current version 8 April 2024. The review of this article was arranged by Associate Editor Giulia Tresca.

Digital Object Identifier 10.1109/OJIA.2024.3366415

# **Analytical Delay Evaluation for FPGA-Based Repetitive Controller in AC Variable Frequency Applications**

# ALESSANDRO FARO <sup>1</sup>, ALESSANDRO LIDOZZI <sup>1</sup> (Member, IEEE), MARCO DI BENEDETTO <sup>(D)</sup><sup>2</sup> (Member, IEEE), LUCA SOLERO <sup>(D)</sup><sup>1</sup> (Senior Member, IEEE), AND STEFANO BIFARETTI<sup>3</sup> (Member, IEEE)

<sup>1</sup>Department of Engineering, Civil, Computer Science and Aeronautical Technologies, ROMA TRE University, 00146 Roma, Italy <sup>2</sup>Department of Industrial, Electronic and Mechanical Engineering, ROMA TRE University, 00146 Roma, Italy <sup>3</sup>Department of Industrial Engineering, University of Roma Tor Vergata, 00133 Roma, Italy

CORRESPONDING AUTHOR: MARCO DI BENEDETTO. (Email: marco.dibenedetto@uniroma3.it)

This work was supported by the Regione Lazio of Italy under Grant "Progetti di Gruppi di Ricerca 2020, 36774."

**ABSTRACT** Repetitive controller provides a very low third harmonic dimension in the quantities under control. It exhibits an inherent issue when operated to track variable frequency references. The article deals with the analysis of the operating conditions when the controller is executed at variable frequency without any resynchronization with respect to the pulsewidth modulation carrier, which is the most common mode of operation. The delays introduced are then evaluated analytically concerning the sampling and output frequency that must be tracked. The proposed analysis allows obtaining the maximum delay affecting the control chain, which was introduced by the repetitive control desynched operation. The knowledge of the delay introduced in the control loops is at the basis of any control tuning procedure and gains selection, even when adaptive control strategies are used.

**INDEX TERMS** Digital control, field programmable gate array (FPGA), repetitive control, variable frequency.

### NOMENCI ATUDE

| <b>NOMENCLATURE</b> $T_{SW}$ Switching and sampling period. |                                                                                                                                    | MCTM <sub>MS</sub>      | Maximum control trigger mismatch of the modulating signals (maximum delay related                                                                        |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| n                                                           | Depth of the Repetitive Control delay line.                                                                                        | ATM <sub>critical</sub> | to the modulating signal update).<br>Acquire Triggers Mismatch Critical (It rep-                                                                         |

| $\Delta T_{ACQ}$                                            | Time required by the sampling and digital conversion, which is related to the analog-to-digital input interface.                   |                         | resents the critical value of the <i>ATM</i> : it will be linked to the <i>MCTM</i> when $MCTM_{MS}$ does not exist; there are no issues in updating the |

| $\Delta T_{MODg}$                                           | Control Algorithm execution time at the end                                                                                        |                         | modulating signals).                                                                                                                                     |

|                                                             | of that the updated modulating signals are available.                                                                              | MST <sub>SW</sub>       | Mismatch immediately Smaller than $T_{SW}$ (Relative Maximum delay within $T_{SW}$ ).                                                                    |

| n <sub>sh</sub>                                             | Initial shift between the pulse width mod-<br>ulation (PWM) synch signal (triggering the<br>sampling of measurements, etc) and the | MMAL                    | Minimum Mismatch Acquiring Lag (Mini-<br>mum time mismatch related to the acquisition<br>of measurements, related to the $T_{SW}$ and                    |

| МСТМ                                                        | Control Algorithm call.<br>Maximum Control Trigger Mismatch (abso-<br>lute maximum value).                                         | ATM <sub>MIN</sub>      | $\Delta T_{ACQ}$ quantities).<br>Acquire Trigger Mismatch Minimum (Complementary with respect T <sub>SW</sub> to <i>MMAL</i> ).                          |

| $CTM_{ATM_{MIN}}$ | Control Trigger Mismatch ATM (It is linked |  |

|-------------------|--------------------------------------------|--|

|                   | to $T_{sw}$ and $ATM_{MIN}$ ).             |  |

| MaxTotDelay       | Maximum delay to be considered for the     |  |

|                   | Control Algorithm.                         |  |

| MTM               | Minimum Triggers Mismatch.                 |  |

## I. INTRODUCTION

Repetitive controller has been widely used in several applications where a sinusoidal reference must be tracked [1], [2], and when the main controllers must be supported for harmonics compensation [3]. In grid-connected [4], [5], stand-alone [6], [7], or electrical drives [8], [9] applications, where the fundamental frequency changes or even in stand-alone mode when the output fundamental harmonic must be modified, a conventional repetitive controller requires an interpolation method or additional memory to achieve the required frequency adaptability. It results in very complicated control structures, which in many cases tend to favor alternative control strategies [10]. On the other hand, repetitive control (RC) could offer much better performance combined with implementation simplicity [11], even including the adoption of digital filter solutions to avoid instabilities [12]. A very straightforward approach is to delink the execution of the RC from the main PWM modulator (i.e., the main scheduler), which represents the main timing. The results are a straightforward control structure that keeps the well known and reliable architecture typical of the RC; however, it is executed at variable frequency. Discrete-time variable-structure RC operating in quasi-sliding mode is presented in [13], verified by simulation only, and resulting in a very complicated implementation. In contrast, a preliminary approach to an adaptive RC for discrete systems is proposed in [14]. In [15], a robust RC based on a causal infinite impulse response (IIR) compensator with time-varying sampling periods is described. However, variable delays are not considered in the implementation. A frequency adaptive proportional RC for grid-connected inverters is proposed in [16], being based on the Thiran all-pass IIR filter. In order to resist to limited grid frequency variation, a multibandwidth RC is proposed in [17], where each of the resonant bandwidth is set individually by an internal model filter. Variable delay estimation when the RC is operated desynchronized from the main scheduler is reported in [18], with the limitation of assuming that the RC loops will be synched to the main scheduler at any frequency variation. The control method proposed in [19] could compensate for the harmonics more accurately with an integer order RC thanks to the high switching and sampling frequency of the adopted SiC devices. Similarly, in [20] and [21], the virtual-variable sampling is proposed to overcome the gain degradation of the RC when operated at a frequency that is different from the rated one. However, in many industrial or cost-effective applications, the usage of wide bandgap devices is not suitable and hence, alternative control solutions must be adopted to take advantage of the RC structure. A specific manipulation of the delay line to overcome the performance degradation of the RC due to the frequency variations of the signal to be tracked is illustrated in [22]. In the presented cases, the RC 118

is executed with a variable period to keep the delay line at a constant depth, hence, the introduced variable delays must be accurately considered. The desynched operation of the RC brings into the control chain a certain amount of variable delay that must be accurately determined before any tuning procedure can be applied.

The proposed analytical approach allows the real-time evaluation of the delay introduced by the use of repetitive controllers with variable frequency and constant delay line. Furthermore, the analytical treatment will allow estimating the instantaneous delay and its maximum value before it is present in the system. That is completely different from a direct measurement with embedded digital counters, as they provide the amount of delay after the delay has already produced its effects on the system.

### **II. SYSTEM DESCRIPTION AND ANALYTICAL APPROACH**

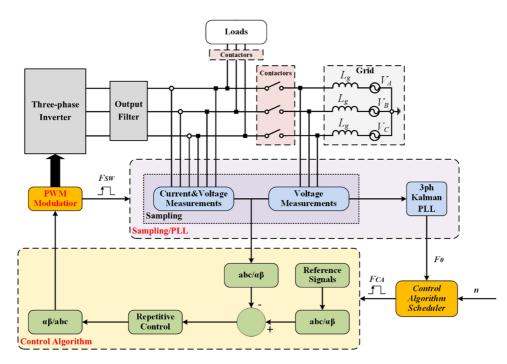

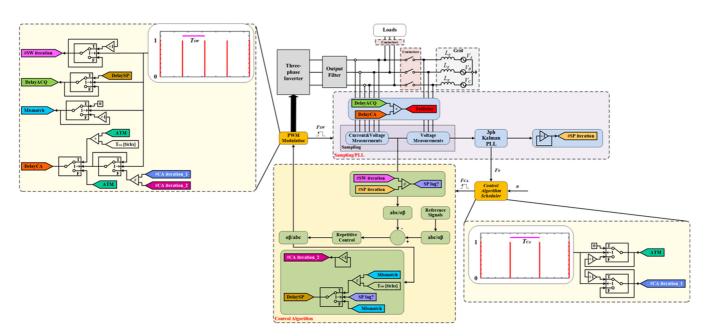

In both grid-tied and intentional islanding operations, the output frequency of the ac signals cannot be considered a constant, nonvarying signal. Hence, the advantages of using the repetitive control are then lost. Fig. 1 illustrates the block scheme of the variable frequency repetitive controller, with a desynched operation concerning the main PWM scheduler [23]. Hence, important considerations must be taken to achieve a comprehensive analysis and then obtain suitable RC parameters tuning. Due to a time shift between the control algorithm (CA) (i.e., the repetitive control) and the PWM synch signal, the delay evaluation is a mandatory task before any tuning considerations. In this method, three loops are realized to execute the CA with a variable frequency, which is generally different from the switching and sampling main frequency.

The first loop contains two decoupled and totally independent structures; the PWM modulator (PWMM) is used to provide opening/closing signals to the inverter's switches and to send the trigger signal to the sampling/PLL block according to the switching frequency.

This guarantees that measure acquisition task samples the instantaneous average value. The CA scheduler has been specifically intended to provide the trigger signal for the CA according to the PLL estimated output fundamental frequency.

As shown in Fig. 1, the CA is tight to the synch signal, which exhibits the same frequency of the PWM modulator only when the output frequency is the rated. In fact, that loop runs at a variable frequency ( $F_{CA}$ ), calculated from the delay line length *n* (i.e., with constant depth) and the output fundamental frequency  $F_0$  usually achieved by a PLL in grid-tied mode of operation (or the desired output frequency when operating in standalone mode):  $F_{CA} = n \cdot F_0$ .

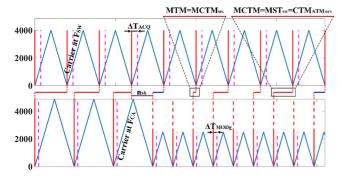

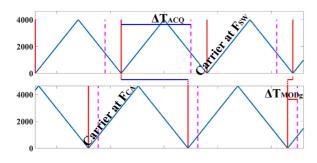

When the CA is running and the fundamental frequency changes, since this variation most probably will occur when the two carrier waveforms are not aligned, the resulting synchronous event could not appear anymore for the new  $F_0$  as it can be noticed from Fig. 2.

FIGURE 1. Block scheme of the frequency adaptive RC.

**FIGURE 2.**  $F_0$  step variation from 41 to 80 Hz when the PWM and control carriers are not aligned.

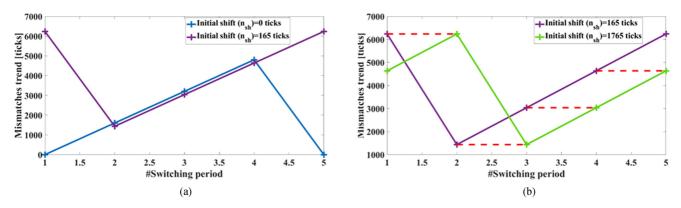

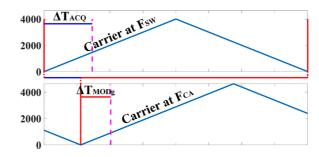

The quantity  $n_{sh}$  is considered as the initial shift, equal to an integer number of ticks ranging from 1 to  $T_{SW}$  (ticks), between the two carrier waveforms (i.e., PWM and sampling) when  $F_{CA}$  is changed due to a  $F_0$  variation. The initial shift is totally random, being related to the history of operation. The proposed analysis has been performed considering an initial shift different from zero, avoiding the ideal case of aligned carriers. The algorithm can only know the range of the shift that goes from 0 to the number of ticks relative to the switching frequency. This will result in a possible alteration of the maximum delay achieved with the two methods presented in [23]. Therefore, a new technique has been developed to provide the maximum delay whatever it is the starting shift  $(n_{sh})$ between the two triggers. As it can be seen from Fig. 4(a), for  $n_{sh} \neq 0$  the mismatches between the PWM modulator trigger and the CA call will assume different values from the case in which synchronism would be present ( $n_{sh} = 0$ ).

However, the typical period of the specific mismatch is maintained after a certain number of switching periods. Moreover, the initial shift  $n_{sh}$  to be considered could be equal to an integer number ranging from 1 to  $T_{SW}$  (*ticks*). However, as shown in Fig. 4(b), for a  $n_{sh}$  greater than the *MTM* at  $n_{sh}$ = 0, the mismatches will assume the same values as for a case of a certain shift lower than the *MTM* at  $n_{sh} = 0$ . In the reported case, the *MTM* at  $n_{sh} = 0$  is equal to 1600 ticks, whereas its general expression is as in (1). Therefore, only  $n_{sh}$ smaller than *MTM* at  $n_{sh} = 0$  can be considered, reducing the possible scenarios that could arise when the synchronism is not present.

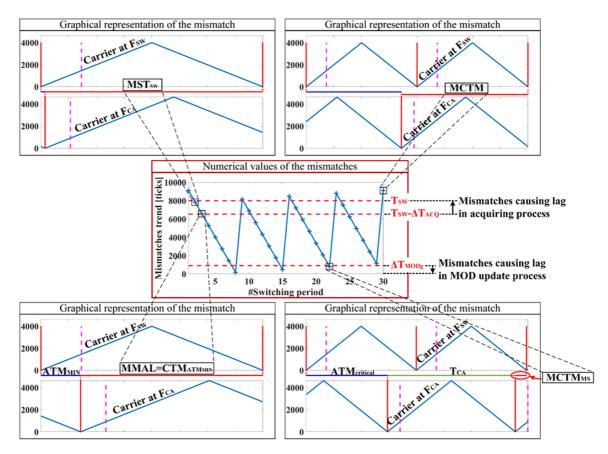

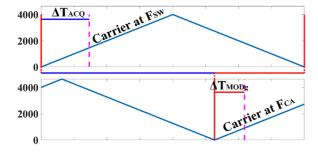

The proposed analysis is based on evaluating the *MTM* quantity, which would be possible by introducing the  $n_{sh}$  parameter and the variables defined in the nomenclature section. Main quantities have been graphically displayed in Fig. 3 and their closed form analytical expressions will be shown in the proposed analysis

$$\begin{bmatrix} \mathbf{M}_{ismatch_{1}} \\ \dots \\ \mathbf{M}_{ismatch_{N}} \end{bmatrix}_{n_{sh_{1}} > MTM|_{n_{sh}=0}} = \begin{bmatrix} \mathbf{M}_{ismatch_{1}} \\ \dots \\ \mathbf{M}_{ismatch_{N}} \end{bmatrix}_{n_{sh_{2}} < MTM|_{n_{sh}=0}}$$

$$n_{sh_{2}} = n_{sh_{1}} - \left\lfloor \frac{n_{sh_{1}}}{MTM|_{n_{sh}=0}} \right\rfloor \cdot MTM|_{n_{sh}=0}.$$

(1)

The image in the center represents the value assumed by the mismatch between the triggers of two adjacent control cycles as the switching period varies. The images on the outside are specific zooms taken from the main plot. As can be seen, the trend is periodic, therefore the initial mismatch is found after N switching periods, with N depending on  $F_{sw}$  and  $F_0$ . To

FIGURE 3. Newly introduced parameters for the most comprehensive MaxTotDelay evaluation.  $F_0 = 43.1$  Hz,  $n_{sh} = 150$  ticks.

**FIGURE 4.** (a) Mismatches trend comparison for  $F_0 = 62.5$  Hz when initial shift changes from 0 ticks to 165 ticks. (b) Mismatches trend comparison for  $F_0 = 62.5$  Hz when initial shift changes from 165 ticks to 1765 ticks.

calculate the *MaxTotDelay*, additional parameters have been introduced, such as the *MCTM*, *MSTSW*, etc.

For each of these values, a zoom has been made to view them through the two carriers. Therefore, the crosses on the central image represent the numerical value of the given parameter which is then zoomed and graphically represented by the distance between the carrier triggers, as reported in the outer plots of Fig. 3. The first parameter to evaluate is the new *MTM* that will be present when the initial *shift* between the two carrier waveforms is different from 0. This value can be rated from

$$MTM|_{n_{sh}} = \left( \left\lfloor \frac{n_{sh}}{MTM|_{n_{sh}}=0} \right\rfloor + 1 \right) \cdot MTM|_{n_{sh}}=0 - n_{sh}.$$

(2)

The *Floor* operator  $\lfloor \rfloor$  returns the integer part without rounding.

The second parameter to be updated is the *MaxTM*. To take into account the possible initial *shift*, the formula that can be

used is the following:

$$MaxTM|_{n_{sh}} = \overbrace{(N-1) \cdot MTM|_{n_{sh}}=0}^{MaxTM|_{n_{sh}}=0} + \left\lfloor \frac{n_{sh}}{MTM|_{n_{sh}}=0} \right\rfloor$$

$$\cdot MTM|_{n_{sh}}=0 - n_{sh} + \left\lceil \frac{\operatorname{mod}\left(n_{sh}, MTM|_{n_{sh}}=0\right)}{T_{SW}} \right\rceil \cdot MTM|_{n_{sh}}=0$$

(3)

*Ceil* operator  $\lceil \rceil$  will provide the nearest greater integer value.

From the updated value of the *MaxTM*, related to the current  $n_{sh}$ , it is possible to rate the maximum value that the mismatch will assume (MCTM)

$$MCTM = MaxTM|_{n_{sh}} + \left\lfloor \frac{MTM|_{n_{sh}}}{MTM|_{n_{sh}=0}} \right\rfloor \cdot MTM|_{n_{sh}=0}.$$

(4)

After updating the parameters previously introduced in [18], where the case with the two carrier waveforms starting aligned was analyzed, additional quantities must be evaluated to give the most general formula for computing the *Max-TotDelay*. First, it is necessary to understand if a mismatch immediately smaller than the  $\Delta t_{MODg}$  arises, and its value. That misalignment, defined as  $MCTM_{MS}$ , will be the greater mismatch for which the modulating signals update will lag. The value can be computed using

$$MCTM_{MS} = \left\lfloor \frac{\Delta t_{MOD_g}}{MTM|_{n_{sh}=0}} \right\rfloor MTM|_{n_{sh}=0} + MTM|_{n_{sh}} - \left\{ 1 - \left\lceil \frac{\Delta t_{MOD_g}}{\frac{\Delta t_{MOD_g}}{MTM|_{n_{sh}=0}} \right\rfloor \cdot MTM|_{n_{sh}=0}}{MTM|_{n_{sh}}} \right\rceil \right\} MTM|_{n_{sh}=0}.$$

$$(5)$$

When there are no time mismatches in the current observation window that are smaller than or equal to  $\Delta t_{MODg}$ , it can be read that the delay in the modulating signals update will not affect any of the switching periods: equation (5) will return a negative or a 0 value. On the contrary, when the time discrepancies are smaller than or equal to  $\Delta t_{MODg}$ , the related switching periods will be affected by the delay of the modulating signals update, which do not receive the last computed value: equation (5) will return the greater of these mismatches. It is then possible to directly identify the previously shown cases by introducing a selector value, which can be expressed as

$$s_1 = \left\lceil \frac{\frac{|MCTM_{MS}| + MCTM_{MS}}{2}}{\Delta t_{MOD_g}} \right\rceil.$$

(6)

The next step is to evaluate the  $ATM_{critical}$  parameter. This value is the *MCTM* paired part when  $s_1$  is 0. In fact, in this case all the switching periods will receive the updated modulating signals without additional delays. On the contrary, when  $s_1$  is equal to 1 it points out that  $ATM_{critical}$  will be the complementary part of  $MCTM_{MS} + T_{CA}$ . In fact, the switching

period related to the  $MCTM_{MS}$  will receive the modulating signals from the previous CA iteration, instead of the current one. It follows that the largest delay related to the modulating signals update process will be equal to the  $MCTM_{MS}$  plus a CA period. The  $ATM_{critical}$  can be evaluated as in

$$ATM_{critical} = \left\lfloor \frac{s_1 (MCTM_{MS} + T_{CA}) + (1 - s_1) MCTM}{T_{SW}} \right\rfloor T_{SW} - \\ + [s_1 (MCTM_{MS} + T_{CA}) + (1 - s_1) MCTM].$$

(7)

To later distinguish the case where the  $ATM_{critical}$  is smaller or equal than  $\Delta t_{ACQ}$  (i.e., the measurement acquisition is lagging the current CA iteration) from the case where the  $ATM_{critical}$  is greater than  $\Delta t_{ACQ}$  (i.e., the measurement acquisition is temporally consistent with the current CA iteration), an additional index could be introduced as shown in the following:

$$s_{2} = \left[ \underbrace{ \left[ \frac{\Delta t_{ACQ}}{ATM_{\text{critical}} + 1 - \left\lceil \frac{ATM_{\text{critical}}}{T_{\text{SW}}} \right\rceil} \right]}_{\Delta t_{ACO}} \right]. \tag{8}$$

The coefficient  $s_2$  will be equal to 0 when  $ATM_{critical}$  will be greater than  $\Delta t_{ACQ}$  (i.e., the current CA iteration will receive the measurements from the last sampling period), while  $s_2$ will be equal to 1 when  $ATM_{critical}$  will be smaller than or equal to  $\Delta t_{ACQ}$  (i.e., the current CA iteration will receive the measurements from the previous sampling, resulting in a lag of the acquiring process).

Concerning the quantities  $\Delta t_{ACQ} = \Delta t_{MODg}$ , totally random values were used, since they depend on how the CA was implemented and on its computational burden. The constraint is that  $\Delta t_{ACQ}$  must not be greater than the sampling time  $(1/F_{sw})$ , otherwise a suitable under sampling would be necessary, keeping valid the proposed theory. Now, since  $F_{SW}$  is theoretically fixed, the upper limit of  $\Delta t_{ACQ}$  is limited by the sampling time.

Concerning  $\Delta t_{MODg}$  however, the procedure takes place with a completely opposite approach. In fact, it depends on how the control is implemented and its value will impose a higher limit on the  $F_{CA}$  frequency that can be used. At this point, four scenarios could arise.

### A. $S_1 = 1 \text{ AND } S_2 = 1$

Since  $s_1 = 1$ , a mismatch called  $MCTM_{MS}$ , and smaller than  $\Delta t_{MODg}$ , exists, as shown in Fig. 5. The CA will not be able to provide the modulating signal for the next switching period, which will apply the previous values. Therefore, the resulting control actions will be loaded and then applied with a delay: formally, a time equal to  $T_{ca}$  is lost.

Moreover, since  $s_2 = 1$ , the  $ATM_{critical}$  is lower than  $\Delta t_{ACQ}$ , as highlighted in Fig. 5. In this case, the  $ATM_{critical}$  is related to the current CA iteration that will provide the updated modulating signals to the switching period that will start after a  $T_{CA}+MCTM_{MS}$  ticks. Moreover, the acquired measurements

FIGURE 5. Graphical illustration of Case A.

FIGURE 6. Graphical illustration of Case B.

will be supplied to the CA after the scheduler has called it. Therefore, the CA will use the samples available from the previous iteration: a  $T_{SW}$  is then lost.

Therefore, the updated control actions are loaded with a delay of a CA period, jointly with a delay due to noncoherent measurements that exhibit a time lag of a sampling period.

#### **B.** $S_1 = 0 AND S_2 = 0$

Since  $s_1 = 0$ , there are no mismatches lower than  $\Delta t_{MODg}$ . Hence, all switching periods will receive the updated and coherent values of the modulating signals. Moreover, since  $s_2 = 0$ , the  $ATM_{critical}$  is not smaller than  $\Delta t_{ACQ}$ . In this case  $ATM_{critical}$  is directly linked to the *MCTM*, being the minimum *ATM*. All the CA calls will be executed with the updated values of the measurements, as highlighted in Fig. 6. There will be no additional delays in the control structure, neither in measurements acquisition nor when loading the updated modulating signals.

#### C. $S_1 = 0 AND S_2 = 1$

Since  $s_1 = 0$  there are no mismatches smaller than  $\Delta t_{MODg}$ . Each CA iteration will end within the current switching cycle, as graphically shown in Fig. 7.

However, since  $s_2 = 1$ , the resulting  $ATM_{critical}$  is lower than  $\Delta t_{ACQ}$ . In this case, the  $ATM_{critical}$  is directly related to the *MCTM*, being the minimum *ATM*). During one or more cycles of the CA the modulating signals will be calculated with measurements that are not consistent with the current control period: the previous cycle quantities will be used, as illustrated in Fig. 7. The effect can be explained by considering that the measures acquisition process ends after the trigger of the CA,

FIGURE 7. Graphical illustration of Case C.

even if started before the CA call. The delay in this case is equal to  $T_{sw}$ .

### **D.** $S_1 = 1 \text{ AND } S_2 = 0$

Since  $s_1 = 1$ , there is an MCTM<sub>MS</sub> mismatch lower than  $\Delta t_{MODg}$ . The control algorithm, whose end is MCTM<sub>MS</sub> ticks before the start of the next switching period and does not close before the next switching period. Therefore, the provided control actions are not related to the last CA call, coming from the previous iteration: a time of  $T_{ca}$  is then lost.

Moreover, since  $s_2 = 0$ , the  $ATM_{critical}$  is not lower than  $\Delta t_{ACQ}$ , the  $ATM_{critical}$  is related to the CA iteration that provides the modulating signals to the switching period that will start after a time equal to  $T_{CA} + MCTM_{MS}$  ticks. The CA related to the mismatch equal to the  $MCTM_{MS}$  will be executed with the consistent measurements' values.

Due to that behavior, it becomes necessary to evaluate the maximum delay, which is related to the switching period affected by the loss of one  $T_{CA}$  or to the switching iteration which exhibits a delay larger to one  $T_{SW}$  or more. Accordingly, it requires the definition of new parameters as follows.

The idea behind is to recognize if there are *ATM* smaller than  $\Delta t_{ACQ}$ . Therefore, the first step is to calculate the smallest *ATM*, which will be related to the largest mismatch still lower than the switching period. Hence, the mismatch immediately smaller than  $T_{SW}$  (*MST*<sub>SW</sub>) must be introduced, and achievable as

$$MST_{SW} = \left( \left\lfloor \frac{(1-s_3) \cdot T_{SW} + s_3 \cdot T_{CA}}{MTM|_{n_{sh}=0}} \right\rfloor - 1 \right) \cdot MTM|_{n_{sh}=0} + MTM|_{n_{sh}}.$$

(9)

where the selector  $s_3$  can be defined as

$$s_{3} = \frac{|M - N| + (M - N)}{2(M - N) + \left(1 - \left\lceil \frac{|M - N|}{M - N} \right\rceil\right)}.$$

(10)

The  $s_3$  parameter is equal to 1 when M is greater than N (i.e.,  $T_{SW}$  results greater than  $T_{CA}$ ). On the contrary,  $s_3$  is equal to 0 when M is smaller than or equal to N (i.e.,  $T_{SW}$  is lower than or equal to  $T_{CA}$ ). The evaluation of the  $MST_{SW}$  parameter in necessary to understand if the complementary value of  $MST_{SW}$  with respect to  $T_{SW}$  is greater, equal, or lower than the measures acquisition time ( $\Delta t_{ACO}$ ).

Therefore, the y parameter is introduced as

$$y = \Delta t_{ACQ} - (T_{SW} - MST_{SW}).$$

(11)

When the quantity y is negative, all the CA iterations will receive samples from the current sampling iteration. On the contrary, when y is positive or equal to 0, at least a CA iteration will receive delayed measurements from the previous call. There is at least a CA iteration lagging the acquiring process. However, after defining the  $MST_{SW}$  and evaluating y, the next step is to evaluate the minimum mismatch for which the delay in the acquisition process will occur (*Minimum Mismatch Acquiring Lag, MMAL*). *MMAL* can be directly achieved by

$$MMAL = MST_{SW} - \left\lfloor \frac{\frac{|y|+y}{2}}{MTM|_{n_{sh}=0}} \right\rfloor MTM|_{n_{sh}=0}.$$

(12)

Notice that

$$\begin{cases} \frac{|y|+y}{2} = 0 \Big|_{\Delta t_{ACQ} \le T_{SW} - MST_{SW}} \\ \frac{|y|+y}{2} > 0 \Big|_{\Delta t_{ACQ} > T_{SW} - MST_{SW}} \end{cases}$$

(13)

Therefore, it will result

$$\begin{split} MMAL &= MST_{\rm SW}|_{\Delta t_{ACQ} - (T_{\rm SW} - MST_{\rm SW}) \le MTM|_{n_{sh} = 0}} \\ MMAL &< MST_{\rm SW}|_{\Delta t_{ACQ} - (T_{\rm SW} - MST_{\rm SW}) > MTM|_{n_{sh} = 0}}. \end{split}$$

(14)

Hence, the  $ATM_{MIN}$ , which is the complementary part of the *MMAL* with respect to  $T_{SW}$ , can be defined as in

$$ATM_{MIN} = T_{SW} - MMAL. \tag{15}$$

Evaluated the  $ATM_{MIN}$ , it is required the introduction of an additional selector  $s_4$ , which will be compared to the  $\Delta t_{ACQ}$  time

$$s_4 = \left[ \underbrace{ \left[ \frac{\Delta t_{ACQ}}{ATM_{MIN} + 1 - \left\lceil \frac{ATM_{MIN}}{T_{SW}} \right\rceil} \right]}_{\Delta t_{ACQ}} \right]$$

(16)

When  $s_4$  is equal to 0,  $ATM_{MIN}$  is greater than  $\Delta t_{ACQ}$  that is, all CA iterations will receive the samples coming from the last sampling period started. When  $s_4$  is equal to 1, the  $ATM_{MIN}$ will be lower than or equal to the  $\Delta t_{ACQ}$  time. Hence, the CA iteration will receive the samples not from the last sampling iteration started but from the previous one with a consequent delay in the acquisition process.

It is also necessary to understand whether there is, and if so, its value, a mismatch greater than  $T_{SW}$ , whose complementary part is equal to the  $ATM_{MIN}$  just calculated. This mismatch will be introduced as  $CTM_{ATM_{MIN}}$  and it can be evaluated as

$$CTM_{ATM_{MIN}} = \left\lfloor \frac{MaxTM_{n_{sh}} - MMAL}{T_{SW}} \right\rfloor \cdot T_{SW} + MMAL.$$

(17)

Finally, the MaxTotDelay can be obtained using

$$MaxTotDelay = (s_2 + 1)T_{SW}$$

$$+ \left\lfloor \frac{s_1 \left( MCTM_{MS} \right) + (1 - s_1) MCTM}{T_{SW}} \right\rfloor T_{SW}$$

$$+ \left[ \left( s_4 + 1 \right) T_{SW} + \left\lfloor \frac{CTM_{ATM_{MIN}}}{T_{SW}} \right\rfloor T_{SW} \right] s_3 \left( 1 - s_2 \right) s_1 s_4$$

$$- \left[ \left( s_2 + 1 \right) T_{SW} + \left\lfloor \frac{s_1 \left( MCTM_{MS} \right) + (1 - s_1) MCTM}{T_{SW}} \right\rfloor T_{SW} \right]$$

$$+ \left\lfloor \frac{s_1 \left( MCTM_{MS} \right) + (1 - s_1) MCTM}{T_{SW}} \right\rfloor T_{SW} \right]$$

$$(18)$$

Equation (18) can be considered as the general formula disregarding the specific case under investigation to obtain the maximum delay, which must be considered in the complete RC action. The value can be computed online, in real time when the algorithm is running, allowing the controller to adapt its gains appropriately. The following steps will be related to the demonstration of the correctness of the proposed analysis by performing a comparison with the direct evaluation of the delays from the field programmable gate array (FPGA).

#### **III. COMPARISON WITH THE SECOND METHOD**

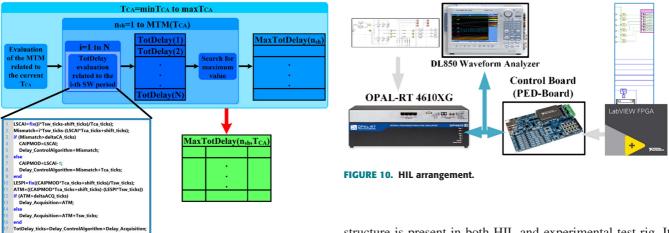

To verify (18), a possible calculation method for the *MaxTot-Delay* has been presented in [18], which has been updated in the present work to take into account the  $n_{sh}$  value, providing a full general expression.

The workflow is reported in Fig. 9. It can be noted that in the shown alternative method, the *MaxTotDelay* correlated with a specific  $T_{CA}$  and a certain  $n_{sh}$ , is evaluated by choosing the maximum value among the *TotDelay* relative to all the *N* switching periods. By varying  $T_{CA}$ , and for each  $T_{CA}$  by varying the value of  $n_{sh}$  from 0 to  $T_{SW}$  [ticks], this alternative technique provides a matrix where one column contains all possible *MaxTotDelay* values which, for a specific  $T_{CA}$ , will occur as a function of the current  $n_{sh}$ .

Therefore, by comparing the data contained in the table obtained with the values provided by (18), it can be demonstrated that the proposed approach provides absolutely consistent results, regardless of the chosen  $T_{CA}$  and  $n_{sh}$  values. In particular, the  $T_{CA}$  varied from 20 to 80 Hz with a step of 0.01 Hz. Furthermore, as already mentioned, for each  $T_{CA}$  also  $n_{sh}$  was varied consistently from 0 to  $MTM|_{n_{sh}=0}$ .

#### **IV. EXPERIMENTAL RESULTS**

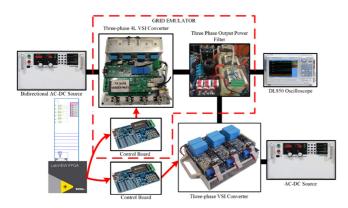

The proposed analytical approach has been verified by a specific Hardware-In-the-Loop real-time testbed based on the OP4610XG high-fidelity solver and a suitable experimental test ring. Hence, the control structure has been implemented in an industrial grade control platform as it would be in a real testing rig. In fact, there are no differences in the control structure between HIL and the experimental setup, which is the basis of the proposed analysis. The variable frequency repetitive controller has been implemented on a Xilinx Artix7 FPGA, which was made available by the PED-Board control board, allowing it to be fully programmable by the

FIGURE 8. Graphical illustration of the subsystems for CA real-time delay evaluation.

FIGURE 9. MaxTotDelay alternative calculation.

LabVIEW development environment. Thanks to the FPGA reconfigurable capabilities, which allows us to create specific counters that can be placed in the exact code position, the quantities already defined in the analytical derivation have been directly evaluated by an accurate delay measurement and analysis directly implemented in the FPGA. Hence, the above expressions were not directly used for delay evaluation. As proof, the FPGA results have been compared with the results achieved by the reported analytical derivation. The proposed validation methodology allows us to use in a future implementation, the illustrated closed form expressions, implemented in a DSP or  $\mu$ Processor, relieving the FPGA space which was dedicated to the measurement of the delays (i.e., about 30% of the total required space). The results have been obtained by adding specific FPGA digital counters having the purpose to evaluate all the delays as shown in Fig. 8. The same code structure is present in both HIL and experimental test-rig. It can be imagined that those parts will be removed in a final implementation, taking advantage of the proposed analytical expressions, which can also be implemented on a  $\mu$ Processor, saving the FPGA space.

The setup used for both HIL verifications and the experimental campaign are shown in Figs. 10 and 11, respectively. In the testbed, the variable frequency ac side has been emulated by a suitable three-phase inverter with output voltage control.

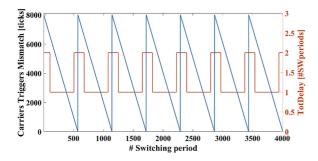

The analytical method has been illustrated and initially compared with the results presented in [18]. The full validation of the proposed closed-form expressions requires the direct comparison with the results achieved when control software runs on an industrial grade control platform. In the experimental setup, the fundamental frequency has been forced to be 49.91265 Hz and imposing  $n_{sh}$  equal to 0. Then, the trend for the *Mismatches* and for the normalized *TotDelay* have been directly achieved as reported in Fig. 12.

After extracting the maximum value from the trend related to the *TotDelay*, the value has been compared with the result

FIGURE 11. Experimental setup.

FIGURE 12. Mismatches and TotDelay(#) trend analytically evaluated.

from (18). By varying  $n_{sh}$  and  $F_0$ , it is then possible to verify the presented method, having the possibility to evaluate the *MaxTotDelay* before it appears in the upcoming iterations. In the next, there will be no distinction between the HIL and the pure experimental results, being the control platform the same, with the same control software. Hence, from the FPGA code updated according to Fig. 8, it was possible to obtain the maximum delay for a given fundamental frequency  $F_0$  and for a specific  $n_{sh}$  coefficient. The reported maximum delay is the quantity seen from the control point of view, directly affecting the system stability and performance.

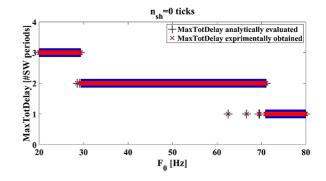

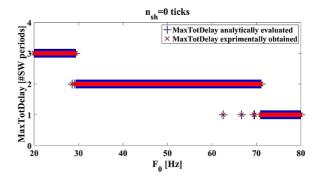

In the following figures, the validity of the proposed closedform expressions and analytical derivation will be proved by comparing the results with the FPGA direct measurements. The fundamental frequency  $F_0$  was varied between 20 and 80 Hz with a step of 0.01 Hz to include noninteger values. Moreover, starting from zero, the  $n_{sh}$  quantity has been varied from 0 to 8000 (with step of 1 ticks), to test all the possible scenarios that could arise, randomly changed, whereas only some results have been reported. Initially, as shown from Fig. 13 the  $n_{sh}$  quantity has been set to zero and the delays have been calculated by the proposed expressions and from the FPGA counters, for different fundamental frequencies. It can be noticed that the results are perfectly overlapped, which proves the validity of the proposed mathematical approach.

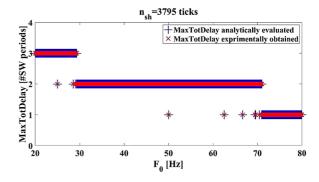

For a more general validation, the results obtained using mathematical expressions or evaluation via the FPGA

**FIGURE 13.** FPGA and analytical *MaxTotDelay* evaluation for  $n_{sh} = 0$  with a frequency resolution of 0.01 Hz.

**FIGURE 14.** FPGA and analytical *MaxTotDelay* evaluation for  $n_{sh} = 1756$  *ticks* with a frequency resolution of 0.01 Hz.

**FIGURE 15.** FPGA and analytical *MaxTotDelay* evaluation for  $n_{sh} = 3795$  *ticks* with a frequency resolution of 0.01 Hz.

counters are also shown, for two random values of  $n_{sh}$ . The results are shown respectively in Fig. 14 for  $n_{sh} = 1756$  ticks and in Fig. 15 for  $n_{sh} = 3795$  ticks. In both cases, the results are perfectly coherent, confirming the correctness of the proposed solution. As can been noticed, varying the  $n_{sh}$  the changing of the *MaxTotDelay*, for a certain  $F_0$ , can be realized. However, the analytic proposed method effectiveness has been proved, leading, as already mentioned, to the possibility to evaluate the *MaxTotDelay* before it appears while the software is running. That is a very fundamental feature. In fact, the CA will be able to adjust its control parameters by evaluating a few simple equations, as soon as the new fundamental frequency occurs, without the need to wait for the switching periods.

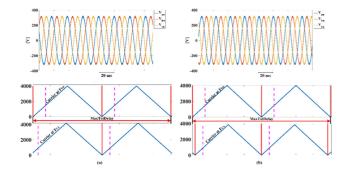

FIGURE 16. Phase voltages, switching and control carriers signals for a narrow frequency variation.

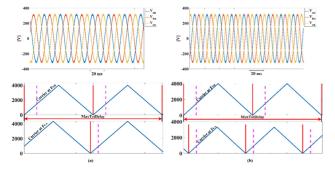

FIGURE 17. Grid voltages and carriers for both switching and control loops.

Hence, with a specific prediction of the future delay due to frequency variation.

Fig. 16(a) shows the phase voltages emulated via the fourleg inverter shown in Fig. 11. The fundamental frequency has been set at 48 Hz. The carriers are represented below where the one at the top is related to the switching frequency, which is imposed and fixed, while the one at the bottom is related to the control frequency proportional to the delay line and the frequency fundamental. These information are used to calculate the *MaxTotDelay*. Coherently, Fig. 16(b) shows the same variables where the grid frequency has been moved to 52 Hz.

Results for a wider and noninteger grid frequency variation have been reported respectively in Fig. 17(a) and (b), where the frequency of the emulated grid has been changed from 46.3 to 60.4 Hz.

# **V. CONCLUSION**

The RC structure operated at variable frequency grants to take advantage of excellent tracking of sinusoidal references. This permits to go beyond RC's weakness related to variable frequency operations, without any noticeable effects in terms of increased computational efforts or memory usage, and still operating with a constant delay line (i.e., straightforward implementation and suitable for FPGA systems). However, unlinking the RC operation to the main PWM scheduler, which represents the main scheduler of most common control structures, leads to a time mismatch between the CA and PWM modulation, which needs to be evaluated to later move on a suitable RC's gain tuning. A deeper investigation has been reported with comprehensive experimental validation. The illustrated complete analytical derivation provides the closed form expressions for real-time delay evaluation applicable to any general operating case. The analytical formulas take the advantage to determine the amount of delay as soon as the PLL (i.e., or any frequency estimation algorithm or internal reference for ac voltage generators) provides the updated frequency, without the need to wait for the counters to be updated, which will introduce an additional delay in updating the control parameters.

#### REFERENCES

- K. Chang, I. Shim, and G. Park, "Adaptive repetitive control for an eccentricity compensation of optical disk drivers," *IEEE Trans. Consum. Electron.*, vol. 52, no. 2, pp. 445–450, May 2006.

- [2] S. T. Navalkar, E. van Solingen, and J.-W. van Wingerden, "Wind tunnel testing of subspace predictive repetitive control for variable pitch wind turbines," *IEEE Trans. Control Syst. Technol.*, vol. 23, no. 6, pp. 2101–2116, Nov. 2015.

- [3] A. Lunardi, E. Conde, J. Assis, L. Meegahapola, D. A. Fernandes, and A. J. Sguarezi Filho, "Repetitive predictive control for current control of grid-connected inverter under distorted voltage conditions," *IEEE Access*, vol. 10, pp. 16931–16941, 2022.

- [4] M. Tang, M. di Benedetto, S. Bifaretti, A. Lidozzi, and P. Zanchetta, "State of the art of repetitive control in power electronics and drive applications," *IEEE Open J. Ind. Appl.*, vol. 3, pp. 13–29, 2022.

- [5] S. Sahoo, S. Prakash, and S. Mishra, "Power quality improvement of grid-connected DC microgrids using repetitive learning-based PLL under abnormal grid conditions," *IEEE Trans. Ind. Appl.*, vol. 54, no. 1, pp. 82–90, Jan./Feb. 2018.

- [6] C. Blanco, F. Tardelli, D. Reigosa, P. Zanchetta, and F. Briz, "Design of a cooperative voltage harmonic compensation strategy for islanded microgrids combining virtual admittance and repetitive controller," *IEEE Trans. Ind. Appl.*, vol. 55, no. 1, pp. 680–688, Jan./Feb. 2019.

- [7] G. A. Ramos, R. I. Ruget, and R. Costa-Castello, "Robust repetitive control of power inverters for standalone operation in DG systems," *IEEE Trans. Energy Convers.*, vol. 35, no. 1, pp. 237–247, Mar. 2020.

- [8] M. Tang, A. Gaeta, A. Formentini, and P. Zanchetta, "A fractional delay variable frequency repetitive control for torque ripple reduction in PMSMs," *IEEE Trans. Ind. Appl.*, vol. 53, no. 6, pp. 5553–5562, Nov./Dec. 2017.

- [9] Y. Liu, S. Cheng, B. Ning, and Y. Li, "Robust model predictive control with simplified repetitive control for electrical machine drives," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4524–4535, May 2019.

- [10] A. L. Julian, G. Oriti, C. Ji, and P. Zanchetta, "Single-phase energy management system operating in islanding mode with repetitive control and active damping," *IEEE Trans. Ind. Appl.*, vol. 54, no. 5, pp. 5163–5172, Sep./Oct. 2018.

- [11] H. Geng, Z. Zheng, T. Zou, B. Chu, and A. Chandra, "Fast repetitive control with harmonic correction loops for shunt active power filter applied in weak grid," *IEEE Trans. Ind. Appl.*, vol. 55, no. 3, pp. 3198–3206, May–Jun. 2019.

- [12] G. Escobar, P. Mattavelli, and M. F. Martinez-Montejano, "Modifications to repetitive-based controllers using FIR filters for practical implementation," in *Proc. IEEE 35th Annu. Conf. Ind. Electron.*, 2009, pp. 3246–3251.

- [13] M. Sun, Y. Wang, and D. Wang, "Variable-structure repetitive control: A discrete-time strategy," *IEEE Trans. Ind. Electron.*, vol. 52, no. 2, pp. 610–616, Apr. 2005.

- [14] Z. Cao and G. F. Ledwich, "Adaptive repetitive control to track variable periodic signals with fixed sampling rate," *IEEE/ASME Trans. Mechatron.*, vol. 7, no. 3, pp. 378–384, Sep. 2002.

- [15] E. Kurniawan, Z. Cao, and Z. Man, "Design of robust repetitive control with time-varying sampling periods," *IEEE Trans. Ind. Electron.*, vol. 61, no. 6, pp. 2834–2841, Jun. 2014.

- [16] J. Ye, L. Liu, J. Xu, and A. Shen, "Frequency adaptive proportionalrepetitive control for grid-connected inverters," *IEEE Trans. Ind. Electron.*, vol. 68, no. 9, pp. 7965–7974, Sep. 2021.

- [17] M. Zhu, Y. Ye, Y. Xiong, and Q. Zhao, "Multibandwidth repetitive control resisting frequency variation in grid-tied inverters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 1, pp. 446–454, Feb. 2022.

- [18] A. Faro, M. D. Benedetto, A. Lidozzi, and L. Solero, "Constant delayline repetitive control analysis for variable frequency operation," *IEEE Open J. Power Electron.*, vol. 3, pp. 481–491, 2022.

- [19] H. Lin, X. Guo, D. Chen, S. Wu, and G. Chen, "A frequency adaptive repetitive control for active power filter with 380V/75A SiCinverter," *IEEE Trans. Ind. Appl.*, vol. 58, no. 4, pp. 5469–5479, Jul./Aug. 2022.

- [20] Z. Liu, K. Zhou, Y. Yang, J. Wang, and B. Zhang, "Frequencyadaptive virtual variable sampling-based selective harmonic repetitive control of power inverters," *IEEE Trans. Ind. Electron.*, vol. 68, no. 11, pp. 11339–11347, Nov. 2021.

- [21] Z. Liu, B. Zhang, K. Zhoue, and J. Wang, "Virtual variable sampling discrete Fourier transform based selective odd-order harmonic repetitive control of DC/AC converters," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 6444–6452, Jul. 2018.

- [22] S. Baek, Y. Cho, and J.-S. Lai, "Average periodic delay-based frequency adaptable repetitive control with a fixed sampling rate and memory of single-phase PFC converters," *IEEE Trans. Power Electron.*, vol. 36, no. 6, pp. 6572–6585, Jun. 2021.

- [23] M. di Benedetto, A. Faro, L. Bigarelli, A. Lidozzi, and L. Solero, "Constant delay-line frequency adaptive repetitive-resonant control for grid-tied and intentional islanding operations," *IEEE Trans. Ind. Appl.*, vol. 59, no. 2, pp. 1944–1955, Mar./Apr. 2023.

**ALESSANDRO FARO** received the master's degree in mechanical and industrial engineering from the ROMA TRE University, Rome, Italy, in 2020. He is currently working toward the Ph.D. degree in mechanical and industrial engineering with the Department of Engineering, ROMA TRE University, C-PED.

His research activity concerns the control aspect for medium voltage power converters in railway applications. This activity involves the use of hardware-in-the-loop real-time simulators and

FPGA-based control platforms.

**ALESSANDRO LIDOZZI** (Member, IEEE) received the electronic engineering degree and the Ph.D. degree in mechanical and industrial engineering from the ROMA TRE University, Rome, Italy, in 2003 and 2007, respectively.

From 2010 to 2017, he was a Researcher with the Department of Engineering, ROMA TRE University; where, since 2017, he has been an Associate Professor. His research interests are mainly focused on power converters and electrical drives real-time modeling and time critical control strate-

gies, medium voltage power conversion systems and development of highperformance control platforms based on combined DSP-FPGA architectures. He is the co-inventor of the PED-Board ecosystem. He is an Associate Editor of IEEE TRANSACTION ON INDUSTRY APPLICATIONS.

**MARCO DI BENEDETTO** (Member, IEEE) received the M.Eng. degree in electronic engineering from the University of Roma Tor Vergata, Rome, Italy, in 2014 and the Ph.D. degree in mechanical and industrial engineering from the ROMA TRE University, Rome, in 2018.

In October 2022, he was an Assistant Professor with ROMA TRE University's Department of Industrial, Electronic, and Mechanical Engineering. His research interests mainly focus on hardware and FPGA control design for power converter

topologies.

Dr. Benedetto was the IEEE IAS Industrial Power Converter Committee secretary. He was an Associate Editor of the IEEE *Open Journal on Industry Applications and Electrical Systems in Transportation.*

**LUCA SOLERO** (Senior Member, IEEE) received the M.Eng. degree in electrical engineering degree from the University of Rome "La Sapienza," Rome, Italy, in 1994.

Since 1996, he has been with the Department of Engineering, University ROMA TRE, where he is currently a Full Professor in charge of teaching courses in the fields of power electronics and electric drives. He has authored or coauthored more than 200 peer-reviewed papers. His current research interests include design and control of

power electronic converters and drives, multiport and multilevel converters.

Dr. Solero is the Past Chair of the IEEE-IAS Industrial Power Converter Committee IPCC (2020–2021). He was an Associate Editor for IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS and for the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN INDUSTRIAL ELECTRONICS. He is the Deputy Editor-in-Chief for the IEEE OPEN JOURNAL OF INDUSTRY APPLICA-TIONS. Since 2022, he has been the Vice Chair of the IEEE-IAS Industrial Power Conversion Systems Department IPCSD. He was the recipient of the IAS-IPCC 2019 First Prize Paper Award and of the IAS-IPCC 2022 Third Prize Paper Award.

**STEFANO BIFARETTI** (Member, IEEE) received the Ph.D. degree in electronic engineering from the University of Rome "Tor Vergata," Rome, Italy, in 2003.

Since 2007, he has been a Research Fellow with the PEMC Group, University of Nottingham, Nottingham, U.K. Since 2015, he has also been an Associate Professor of power electronics and electrical drives with the Department of Industrial Engineering, University of Rome "Tor Vergata." He has authored or coauthored more than 100 pa-

pers in international journals and conference proceedings. His recent research interests include the design, modeling, and control of power electronics multiport multilevel converters, solid-state transformers, fast charging stations, and high-power supplies for nuclear fusion energy generators.

Dr. Bifaretti is the Transactions Papers Review Chair for the L&S Industrial Power Converters Committee for the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS.